在半导体技术持续追求更高性能、更低功耗与更小尺寸的宏大叙事中,封装技术正扮演着愈发关键的角色。全球晶圆代工龙头台积电(TSMC)宣布其先进的3D堆栈封装技术已进入测试阶段,并传出科技巨头谷歌(Google)与芯片设计公司AMD有望成为其首批客户。这一进展不仅标志着半导体制造工艺的又一次重要突破,也为未来计算机软硬件的协同开发与性能跃升铺平了道路。

技术突破:超越平面封装的维度革命

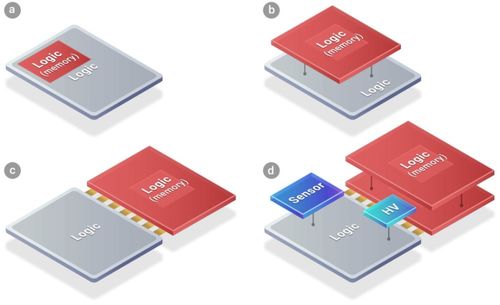

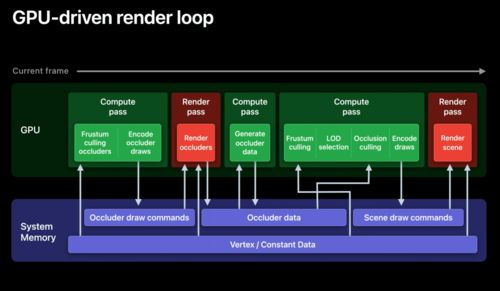

传统的芯片封装技术主要是在二维平面上布局晶体管和互连。随着摩尔定律的推进逐渐面临物理与成本极限,业界开始将目光转向第三维度。台积电的3D堆栈封装技术,如SoIC(系统整合芯片)和CoWoS(基板上晶圆上芯片封装)的演进版本,允许将多个芯片(如处理器、内存、高速缓存等)像搭积木一样在垂直方向上进行堆叠和紧密集成。

这种技术的核心优势在于:

- 极致互连密度与带宽:通过微米级甚至更小间距的硅通孔(TSV)等技术实现芯片间的垂直互连,极大缩短了信号传输路径,显著提升了数据传输带宽并降低了延迟。

- 异构集成能力:能够将采用不同制程节点、不同功能、甚至来自不同制造商的芯片(例如,逻辑芯片、高带宽内存、AI加速器、射频模块等)集成在一个封装体内,实现“超越摩尔”的性能提升。

- 系统级优化:在更小的物理空间内整合更多功能,有助于实现更紧凑的设备设计、更高的能效比以及更优的系统级性能。

客户动向:谷歌与AMD的先锋角色

据报道,谷歌和AMD正与台积电紧密合作,测试并可能率先采用其3D堆栈封装技术,这背后反映了各自清晰的战略需求:

- 谷歌:作为全球云计算与人工智能的领军者,谷歌对数据中心服务器的计算密度、能效和AI推理/训练性能有着近乎苛刻的要求。采用3D堆栈封装的定制化张量处理单元(TPU)或与其他内存芯片的集成方案,可以为其搜索引擎、广告系统、YouTube以及前沿的AI模型(如Gemini)提供更强大、更高效的基础设施支持,巩固其云端竞争优势。

- AMD:在CPU与GPU市场与英特尔和英伟达激烈竞争的AMD,一直致力于通过先进的封装技术提升产品竞争力。其已有的Chiplet(小芯片)设计哲学与3D堆栈技术天然契合。AMD有可能利用该技术将更大容量的3D V-Cache(三维高速缓存)堆叠在CPU核心之上,或将GPU核心与高带宽内存(HBM)更紧密地结合,从而为游戏、数据中心和高性能计算市场带来颠覆性的产品,例如下一代Instinct加速卡或Ryzen/EPYC处理器。

成为首批客户,意味着谷歌与AMD将在技术早期获得关键的设计协同优势和性能红利,但也需共同克服初期在良率、热管理、测试复杂度以及成本方面的挑战。

深远影响:软硬件协同开发的新范式

台积电3D堆栈封装技术的成熟与普及,将深刻改变计算机软硬件技术开发的格局:

- 硬件设计范式转变:从追求单一芯片的工艺微缩,转向基于系统架构的异质集成与协同设计。硬件开发者需要更早、更深入地考虑芯片间互连、功耗分布、散热方案以及信号完整性等系统级问题。

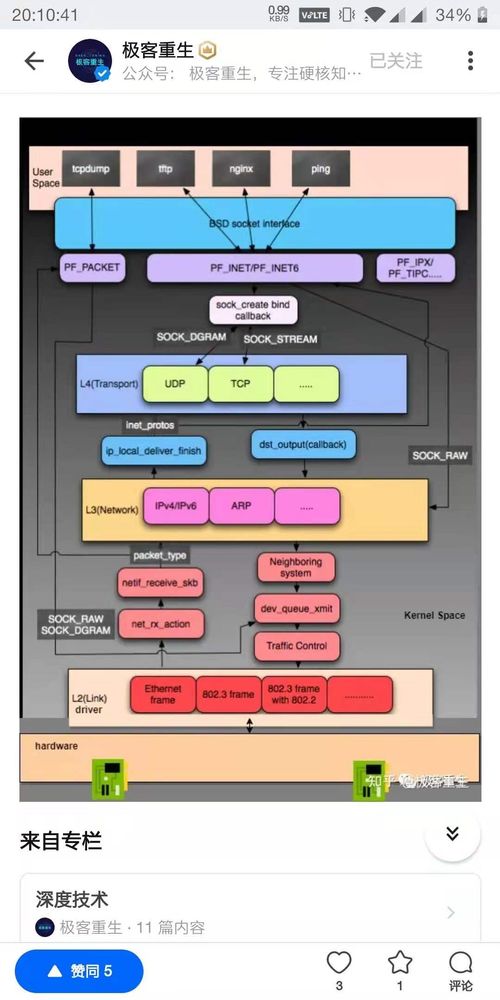

- 软件与系统优化的新前沿:当硬件以高度集成的“系统级封装”形式出现时,操作系统、编译器、驱动程序以及应用程序都需要进行相应的优化以充分释放其潜力。例如,软件需要能够感知并调度不同堆叠层上的计算与存储资源,管理更复杂的非统一内存访问(NUMA)架构,以及利用极高的内存带宽进行并行处理。这对于AI框架、大数据分析、科学计算等软件至关重要。

- 生态合作更加紧密:成功的3D堆栈产品需要晶圆代工厂(如台积电)、芯片设计公司(如AMD)、IP提供商、EDA工具商、封装材料供应商以及终端系统厂商(如谷歌)之间前所未有的深度协作。一个开放、高效的产业生态将成为竞争的关键。

- 应用场景拓展:除了高性能计算和云计算,该技术也将推动智能手机(实现更强大的AI功能)、自动驾驶汽车(集成感知、决策芯片)、物联网设备等对尺寸、功耗敏感领域的技术进步。

###

台积电3D堆栈封装技术步入测试阶段,并吸引谷歌、AMD等行业巨头垂青,是半导体产业向三维集成时代迈进的一个鲜明信号。这不仅仅是制造工艺的升级,更是一场从硬件架构到软件生态的连锁革命。它预示着未来的计算设备将不再仅仅依赖于晶体管尺寸的缩小,而是通过多维度的集成与协同创新,持续驱动数字世界的性能边界。对于计算机软硬件开发者而言,拥抱这一趋势,深入理解并参与系统级的设计与优化,将是赢得下一个计算时代的关键。